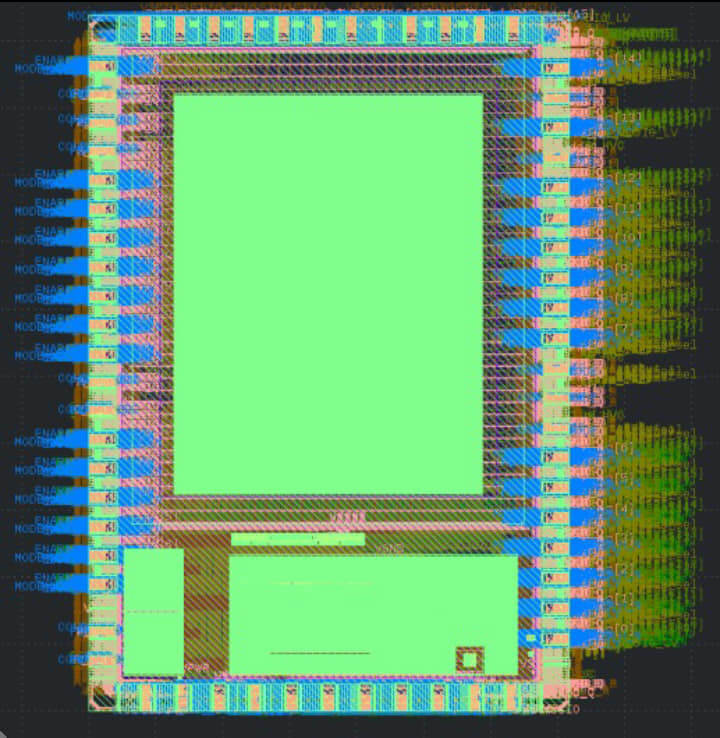

GHAZI (غازی)

The team behind the RTL (Register Transfer Level), APR (Placement and Routing) and both Pre and Post Synthesis Verification of Ghazi System on a Chip. Uses of a core in deeply embedded systems such as IoT end-nodes range from simple control and interaction with peripherals, to the execution of light-weight processing, all the way up to the computation of complex signal processing algorithms. Design of such cores usually involves high royalty fee and copyright implications when using ARM or Intel x86 based architecture. Thus, an SoC, that uses a core based on an open source ISA (Instruction Set Architecture) is often required that we could easily adapt to suit multiple specifications as needed.

- Mentors:

- Dr. Ali Ahmed